作者 杜建宇1,唐睿1,张晓宇2,杨宇驰1,张铁宾1,吕佩珏1,郑德印1,杨宇东1,张驰1,姬峰2,余怀强3,张锦文1,王玮1

单位 1. 北京大学集成电路学院;2. 北京遥感设备研究所;3. 中国电子科技集团公司第二十六研究所

原位 DOI:10.16257/j.cnki.1681-1070.2023.0071

摘要:以 GaN 为代表的新一代半导体材料具有宽禁带、高电子饱和速率、高击穿场强等优异的电学性能,使得射频、电力电子器件有了具备更高功率能力的可能,目前限制器件功率提升的主要瓶颈是缺少与之匹配的散热手段。具有极高热导率的金刚石已成为提升器件散热能力的重要材料,学术界针对金刚石与功率器件集成的先进热管理技术已经开展了大量有益的研究与探索,但是由于金刚石具有极强的化学惰性和超高的硬度,在实际集成和工艺加工过程中,金刚石-GaN 界面容易出现热性能和可靠性问题,甚至会导致器件失效。对金刚石热管理技术的研究进展和存在的问题 进行了深入分析,并对未来主要工作方向做了展望。

关键词:热管理;功率器件;金刚石;嵌入式冷却

01引言

以 GaN 为代表的Ⅲ-Ⅴ族氮化物半导体材料在击穿电压、开关速度等关键电学参数上较 Si 材料有着巨大的性能优势,广泛应用于雷达、电子战系统、蜂巢式基地台、气象卫星和通信卫星等领域,以进一步增强器件的功率密度和提高转换效率。

使用 GaN 材料制备的高电子迁移率晶体管(HEMT)设备可以提供比现有Si 技术超 10 倍的功率密度。这种巨大的功率密度会在发热结区域产生大量的热,且多以热点的形式出现,这种晶体管级别热点的局部热流密度可能超过 10 k W/cm2,若不能将热量有效地导出至外界,热量积累造成的高温会严重影响器件使用寿命、可靠性和性能表现,甚至造成芯片的烧毁失效。

由于传统封装散热能力较低的限制,目前 GaN 器件只能发挥其20%~30%的理论性能;随着功率器件工作温度的升高,功率器件的失效概率呈指数级增长。由此可见,传统 GaN 射频器件封装带来的低散热能力严重影响了射频器件的电学性能和工作可靠性。

金刚石具有的超高热导率使其成为了理想的导热基板,然而,受制于金刚石的超高硬度、高化学惰性、热膨胀系数等性质,金刚石热扩散衬底的集成工艺和金刚石微通道加工工艺都具有较大难度。

本文总结了近年来关于金刚石热扩散衬底集成与金刚石微通道微纳加工技术的发展情况,并对未来金刚石散热衬底的发展进行了分析和展望。

02基于高导热金刚石的热扩散层及其微纳加工技术

传统 GaN 器件的散热路径如图 1(a)所示,热点位于栅极下方,其热流会通过 GaN 外延层、氮化铝(AlN)成核层等多个层间材料扩散至基底中。目前,GaN 基器件多是生长于蓝宝石、Si 或 SiC 衬底上,这些衬底的热导率相对较低,分别为 35 W/(m·K)、150 W/(m·K)、400 W/(m·K),无法满足器件严苛的热管理需求,因此需要在芯片热点近结区集成热导率高的材料来控制器件的温升。

图1 GaN 基 HEMT 器件的散热路径

金刚石具有优异的绝缘性和超高的热导率,单晶金刚石在室温下的导热系数高达 2400 W/(m·K),多晶金刚石在室温下的导热系数接近 2000 W/(m·K),是 GaN 基器件的理想衬底材料。所以热源与金刚石集成后,凭借金刚石的超高热导率,热源产生的热量会迅速地横向扩散在基板内,提升了热源与外界的有效换热面积,从而可以极大地提升系统的换热能力。金刚石基 GaN 器件的散热路径如图 1(b)所示。

此外,为了进一步加强器件的热管理性能,也有学者将嵌入式微流体冷却技术的高换热能力与金刚石的高导热能力结合起来。带微流体的金刚石基 GaN 器件的散热路径如图 1(c)所示,在器件的金刚石衬底上加工微通道,将冷却工质引入至近结区,以期实现更强的热管理能力。

对于金刚石基 GaN 技术的研究,按照研究思路大致分为以下 2 种途径:一是基于沉积生长工艺,在GaN 器件上生长金刚石材质或是在金刚石上外延生长 GaN 器件层,以完成热扩散层的集成;二是基于键合工艺,为了降低器件的界面热阻,在低温甚至是室温下,将化学气相沉积(CVD)生长的金刚石基板与GaN 器件层进行键合。

2.1 基于沉积工艺的金刚石基 GaN 集成

2.1.1 GaN 基底生长金刚石技术

2014 年,美国 Element 公司 (原 Group4 Labs)的BABIC 等开发了直接在外延生长的 GaN 基片上生长金刚石的工艺。首先在高阻 Si 衬底上生长Al GaN/GaN 的器件层,由于 GaN 上直接生长金刚石通常需要富氢环境(氢的体积分数为 95%~99%)和较高的生长温度(700℃以上),此时 GaN 晶圆受到刻蚀,导致在 GaN-金刚石界面形成空洞和缺陷,进而增加了额外的热阻。

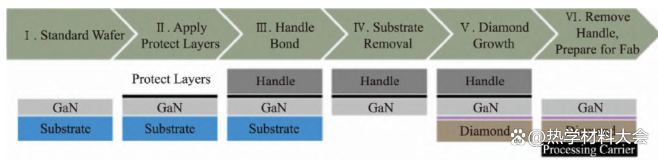

因此,需要一层介质来保护 GaN 外延层。随后晶圆被倒装安装在临时处理片上。之后再去除晶圆下方的 Si 和一些氮化物过渡层,并在暴露的 GaN缓冲层上沉积 50 nm 的介电层,使用热灯丝化学气相沉积(HFCVD)工艺在其上方生长 100 μm 的金刚石,最后从临时处理片上取下金刚石并去除氮化硅保护层,使用衬底移除的工艺在外延 GaN 上直接生长金刚石的具体流程如图 2 所示。

图2 使用衬底移除工艺在外延 GaN 上直接生长金刚石的流程

该方法的关键在于金刚石的生长质量,多晶金刚石通常以晶柱的方式生长,在成核的表面迅速形成具有较小尺寸的晶粒。由于声子在晶界处的散射和吸收,晶核形成过程中的大量晶界无序或错乱的现象将对导热性能产生较大的影响。因此,在界面热阻没有公认理论模型的情况下,必须通过实验来测定不同生长工艺生长的金刚石产生的界面热阻值。

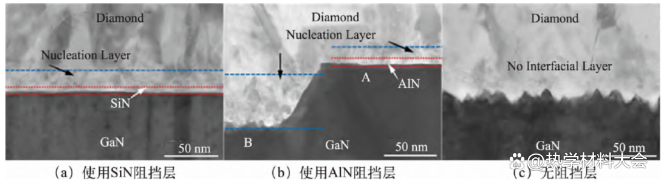

2017 年,英国 Bristol 大学设备热成像与可靠性中心(CDTR)的 ZHOU 等比较了 GaN/SiC 直接生长与分别使用 SiN 或 AlN 作为 GaN 和金刚石的阻挡层3 种加工手段产生的界面热阻,结果如图 3 所示。

图3 阻挡层分别为 SiN、AlN 以及无阻挡层的界面热阻比较

以SiC 衬底上 500 nm 厚的 GaN 层为衬底,在 GaN 上生长了 5 nm 厚的非晶态 SiN 或 AlN 阻挡层,在氢气、氩气、甲烷(体积分数为 0.1%~1%)的气体氛围中,利用微波等离子体化学气相沉积技术(MPCVD),在微波输入功率为 2000~2500 W 的工况下,淀积了厚度约为 1 μm 的多晶金刚石层。由于金刚石 /SiN/GaN 样品产生了粗糙度极低的光滑界面,该金刚石基 GaN 具有已知报道的最低界面热阻(TBR),约为 6.5 m2·K/GW。

2.1.2 金刚石基底生长 GaN 技术

金刚石基 GaN 结构的制备还可以通过在金刚石基底上生长 GaN 来实现。用于加工器件的 GaN 层需要具有足够高的二维电子气(2DEG)迁移率和面载流子密度,这要求外延生长的 GaN 层需要具有良好的晶体取向一致性、低的位错密度、尽可能少且小的表面裂纹以及较低的表面粗糙度。

但是 GaN和金刚石的固有材料属性使外延生长工艺难度较大:①金刚石与 GaN 有较大的晶格失配度(约 13%),这容易导致外延生长的 GaN 具有较大的位错密度,晶体质量不佳;②2 种材料间的热膨胀系数(CTE)差别较大,金刚石的 CTE 约为 0.8×10-6K-1,而 GaN 不同方向的 CTE αa=5.6×10-6K-1,αc=3.2×10-6K-1,CTE 失配将产生严重的界面热应力,可能导致 GaN 外延层的开裂、脱落;③当外延生长衬底为多晶金刚石时,GaN 与衬底之间没有固定的晶格外延关系,外延生长会产生多个不同取向的晶畴,得到连续的 GaN 晶体会更困难。

综上所述,由于材料的特点,相比在 GaN 基底上生长金刚石,在金刚石基底上生长高质量 GaN 需要克服更多的困难,因此近年来的相关研究较少。

早在 2003 年,HAGEMAN 等使用金属有机物化学气相沉积工艺(MOCVD),利用 AlN 作为形核层,在(110)方向的单晶金刚石上沉积初始 GaN 层后,再通过氢化物气相外延工艺(HVPE)使 GaN 晶粒长大,从而在金刚石上生长了厚度超过 100 μm 的多晶 GaN层。这是最早关于金刚石上外延生长 GaN 的报道。

后续十几年,各种在金刚石上外延生长 GaN 的方法被不断探索,为了避免 GaN 晶体的高度无序,保证 GaN 层的电学性能,通常需要一个 Si (111)层或 SixN 层作为外延生长的介质层,但这种低热导率的介质层也阻碍了热量的传递,并且介质层的制备也增加了工艺的复杂度。

2020 年,德克萨斯州立大学的 AHMED 等使用侧向外延生长工艺(ELO)成功从图形化的金刚石开口中外延生长出连续的 GaN 薄膜,实现金刚石基 GaN结构,其过程和结果如图 4 所示。该课题组首先在 SiN上选择性地沉积金刚石纳米晶粒,使用刻蚀方法使SiN 开口以暴露出 GaN 层,利用该层 GaN 的晶体结构,使用 MOCVD 工艺在其上方外延生长成质量良好的器件层。

图4 侧向外延生长制备的金刚石基 GaN 结构

2.1.3 金刚石过孔

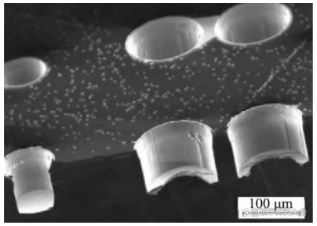

金刚石过孔是由美国 Northrop Grumman AS 公司开发的一种可以改善基底原本散热性能的方法。由于直接在 SiC 基 GaN 的晶圆上整面生长金刚石会产生热应力问题,高温下多层材料的热膨胀系数不匹配会导致晶圆弯曲甚至破裂,极大地增加了正面光刻和正面器件的处理难度,降低了器件可靠性。

于是,研究人员在热源下方对应的 SiC 衬底背面刻蚀深孔,然后通过 MPCVD 技术将金刚石的颗粒沉积在孔中,图 5为选择性生长的金刚石孔 SEM 图,之后使用基于氧的等离子体刻蚀工艺去除其他区域的金刚石薄膜,通过这种方式不断增加孔中的金刚石厚度。该方法可以有效减小金刚石在 GaN 上生长的热应力不匹配问题,减小晶圆的翘曲,使热点局部微米级范围内的基底热导率达到 1500 W/(m·K),界面热阻小于10 m2·K/GW。

图5 选择性生长的金刚石孔 SEM 图

2.1.4 金刚石散热钝化层技术

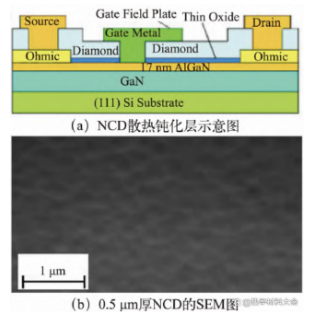

金刚石材料不仅可以作为衬底材料降低 GaN 器件的结温,由于其具有优良的绝缘特性,多晶金刚石还可以作为散热钝化层直接淀积在器件顶部以增强热点顶部的热扩散,同样可以起到增大换热面积的作用。

2012 年,美国海军研究实验室(NRL)的 TADJER等成功在 GaN 基 HEMT 顶部制备了高热导率纳米金刚石薄膜(NCD)以取代热导率较低的 Si3N4钝化层,器件结构如图 6(a)所示。这种工艺首先需要使用等离子增强化学气相沉积(PECVD)在器件表面制备50 nm 的 SiO2作为 NCD 的阻挡层,之后在 750℃下以 100 nm/h 的速度生长 0.5 μm 的 NCD,图 6(b)为其SEM 图。经过实测,NCD 散热钝化层的散热性能比SiN 钝化层更好,使器件的工作温度下降了 20%。

图6 顶部集成金刚石的 GaN 基 HEMT

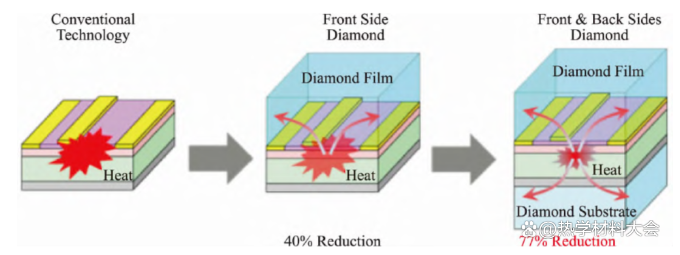

2019 年,日本富士通公司报道了一种在 GaN 基HEMT 器件表面生长高散热性能的金刚石薄膜的方法,生长的金刚石在特定晶相上具有微米尺度的晶粒。该团队在制备好的金刚石散热钝化层器件的背面键合了高导热金刚石散热衬底,制作了金刚石-GaN-金刚石的双层金刚石散热结构,传统封装结构、单层金刚石散热钝化层结构与双层金刚石散热结构对比如图 7 所示。经过测试,这种双层金刚石方案具有优异的散热性能,热点结温较传统封装下降了 77%。

图7 传统封装结构、单层金刚石散热钝化层结构与双层金刚石散热结构对比

2.2 GaN 集成

尽管实验结果已证明使用生长淀积制备金刚石基 GaN 器件的方法可行,但由于生长工艺多是在高温环境中进行,容易产生热应力失配等问题,热应力失配会导致器件在材料相交界面处有较大的晶格失配,引起较大的界面热阻,从而导致金刚石丧失其超高热导率的优势。

且高温工艺下产生的翘曲会增加器件的后续工艺加工难度,影响工艺质量和生产良率。所以近年来有大量研究聚焦于 GaN 与金刚石基板键合集成技术,并为了减小高温键合工艺中热应力的影响,着重开发了低温键合技术。

2.2.1 化合物半导体材料的键合工艺

1990 年,麻省理工学院林肯实验室的 LIAU 等使用了热键合的方法成功键合了厘米级大小的Ⅲ-Ⅴ族半导体材料晶圆,并产生了具有正常二极管特性的PN 结,证明了化合物半导体材料键合的可行性。

之后GaN 在高阻 Si 衬底上的制备工艺日渐成熟,由于 Si衬底易去除的特性,可以获得质量更好的 GaN 晶体用于键合。键合工艺的优势之一是键合前的材料都可以使用最适合的方式进行生长淀积,键合材料的质量得到了保证,可以最大程度保证金刚石的高热导率和 GaN材料优异的电学性能,因此键合成为了制备金刚石基GaN 器件的重要发展方向。

但是由于金刚石和 GaN 之间热膨胀系数的不同,在高温下键合产生的热失配较大,会导致严重的界面热阻和可靠性问题,因此近年来许多研究致力于低温下键合工艺的开发与探索。

2.2.2 低温键合工艺

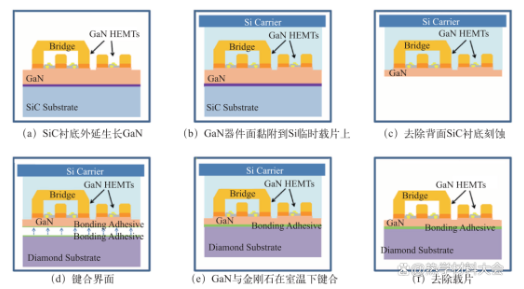

在美国国防部高级研究计划局(DARPA)的项目支持下,BAE 的 CHAO 等开发了一种低温亲水键合工艺,其流程如图 8 所示。

图8 金刚石与 GaN 的亲水键合工艺流程

采用 CMP 工艺对裸露出来的键合面进行化学机械抛光,待其均方根表面粗糙度小于 1 nm 后,在金刚石基板和 GaN 的键合面上沉积一层薄薄的黏附层,在室温下使两侧紧密接触以进行键合。根据红外成像和漏电流瞬态的结果,金刚石衬底上的 GaN HEMT 器件可以在 10 GHz 工作,最大连续射频波(CW)功率密度为 11.0 W/mm,功率附加效率(PAE)为 51%,功率密度比 SiC 基器件行业标准高3.6 倍。但这种方法制备的金刚石基 GaN 结构的界面热阻较大,达 34 m2·K/GW,这可能是由低温亲水键合导致,键合机制容易产生空洞。

2017 年,南京电子设备研究所的 LIU 等也使用亲水键合工艺制备了 3 英寸的金刚石基 GaN 器件晶圆,在 180℃下实现 GaN 基 HEMT 层与金刚石衬底的键合。键合后的 GaN 基 HEMT 器件很好地保持了直流和功率性能,最大电流密度为 1005 mA/mm,在10 GHz 时 CW 功率密度达到了 5.5 W/mm ,PAE 为50.5%。发热结到封装体表面散热热阻降低 20%,峰值温度由 241℃降低到 191℃。

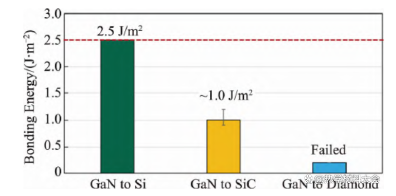

日本学者 SUGA 等从 20 世纪 80 年代末开始研究超高真空(UHV)键合,在后续 20 年间取得了长足的进步,该团队使用表面活化键合技术(SAB)实现了金刚石和 GaN 的室温键合,该方法的显著优势是避免了在键合过程中出现的热失配和界面空洞,因此理论上可以显著降低金刚石-GaN 的界面热阻。然而在SAB 方法中 Ar 离子的轰击会导致 GaN 表面富含 Ga,金刚石表面则会形成非晶的 C 结构,而 C 和 Ga 几乎不存在化学作用,难以实现 GaN-金刚石的键合。使用SAB 方法键合不同材料的键合强度如图 9 所示。这为GaN 与金刚石的键合带来了一种新的思路,Si 或其他活性金属可以成为改善 GaN 与金刚石 SAB 键合的介质层。

图9 使用 SAB 方法将 GaN 与 Si、Si C 和金刚石衬底键合的强度比较

该团队后续用 Si 纳米黏附层改善了 SAB 方法,并在含 Si 的 Ar 离子束轰击下实现了室温下 GaN-金刚石的直接键合。将 2 颗分别使用 CVD 和高温高压(HPHT)工艺生长的单晶金刚石键合到 GaN 薄膜上,GaN 和金刚石表面的均方根粗糙度分别为 0.4 nm和 0.3 nm。其中,CVD 金刚石利用溅射 Si 的纳米黏附层键合,采用特殊设计的离子束源产生的含 Si 的 Ar离子束作用于 HPHT 工艺生长的金刚石来改进 SAB方法。

利用时域热反射(TDTR)方法测得键合界面的界面热阻分别为 18.9 m2·K/GW 和 10.9 m2·K/GW,明显高于用传统高温方法键合的 GaN-金刚石结构。理论分析结果表明,假定器件的最高工作温度为 250℃,使用这种方法集成的金刚石基 GaN 器件可以实现的最大功率是 SiC 基 GaN 器件的 2.5 倍,是 Si 基 GaN器件的 5.4 倍。

2.3 金刚石基 GaN 器件的界面热阻

金刚石的集成对于高功率 HEMT 器件的散热能力提升十分重要,但是金刚石与 GaN 之间较大的晶格失配使得金刚石较传统的 Si C 基底来说更难集成。集成质量不佳会导致材料分界面处产生较大的界面热阻,过大的界面热阻甚至会抵消金刚石的高导热优势,因此如何提高集成质量、减小界面热阻成为了金刚石集成工艺开发的重要研究方向。

GaN-金刚石界面的界面热阻产生机理如图 10 所示,主要包括 3 种微观机制:一是 GaN 和衬底过渡层之间的声子散射;二是过渡层内生成的点缺陷、位错和其他缺陷导致的声子散射;三是 GaN 和衬底中近界面的声子无序散射。

图10 金刚石与 GaN 器件的界面热阻产生机理

这3 种机制导致声子在金刚石-GaN 界面的传导受阻,宏观上体现为界面热阻的上升。有学者研究了界面热阻对于 GaN 基器件散热能力的影响,较大的界面热阻会导致器件的温度升高数十摄氏度,是导致器件温升的主要因素之一。

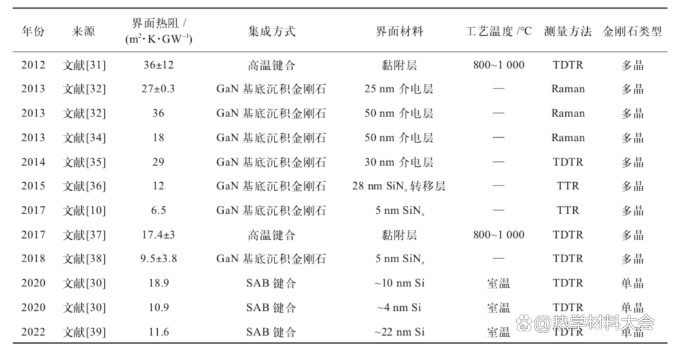

降低金刚石-GaN 界面热阻是集成方法优化迭代的重要方向,近年来由于逐渐开发的低温工艺和转移生长工艺,金刚石-GaN 的界面热阻有了巨大的改善,表 1 展示了近年来文献报道的金刚石基 GaN 器件的界面热阻,可以看到,随着集成工艺手段的不断提升,界面热阻得到了巨大的改善。通过表面活化的低温键合、添加纳米黏附层等方法所制备的金刚石-GaN 器件有着相对较小的界面热阻,并可以实现晶圆级别的加工。但是金刚石-GaN 器件的集成机理有待进一步探索,针对界面处的复杂应力问题、微观失效机理等方面的研究亟需新的发现和突破。

表1 金刚石-GaN 的界面热阻

03金刚石微通道及其微纳加工技术

学界和业界已经在沉积、键合以及界面热阻优化等方面对于 GaN 和金刚石散热集成热管理技术的研究取得了突破性进展,由功率器件产生的热量可以高效地传导至金刚石散热基板内并迅速扩散开,但散热中的另一个问题仍未解决,就是如何将散出的热量从整个器件中带走。因此,许多研究团队想将金刚石基GaN 器件与嵌入式微流体冷却技术结合起来,在集成的金刚石衬底上制备微通道。但金刚石也是自然界中已知最难加工的材料之一,其不仅具有超高的硬度,且几乎对所有的化学物质都有很高的耐性。因此,想在金刚石上制作具有高深宽比、高内壁垂直度、复杂形状的散热微通道结构是一项巨大的挑战。

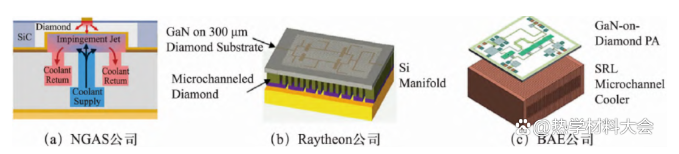

DARPA 从 2012 年开始启动芯片内/芯片间增强冷却(ICECool)研究计划,通过嵌入冷却液介质通道的方式在金刚石基板内进行强制对流散热,从而实现更高的散热能力,即采用金刚石基 GaN 的嵌入式微流体冷却技术将热量转移到冷却液中带走。

在 ICECool项目的资助下,有多家研究团队开展了该技术的开发。国外代表性研究机构基于金刚石微通道进行的不同探索如图 11 所示。

图11 国外代表性研究机构基于金刚石微通道进行的不同探索

美国 NGAS 公司采用金刚石过孔与射流冷却技术结合的方法,首先在 SiC 基底的背面选择性刻蚀过孔,使孔处于热点的下方,之后在孔内沉积金刚石,同时集成了一层 Si 基板射流微通道结构,该结构可以使冷却工质直接冲击金刚石,利用射流滞止区强大的对流换热能力有效地将热量带走。

美国的 Raytheon 公司直接在金刚石基底上刻蚀微通道,并在微通道的下方集成 Si 基的歧管来散热。美国的 BAE 公司在制备好金刚石基 GaN 器件后,将其贴附在金属微流道基板上进行器件的冷却。

针对金刚石微流道加工困难的问题,目前有“增材制造”和“减材制造”2 种加工思路,其中增材思路主要是在现有微流道基础上进行金刚石的沉积,通过覆形的方式加工出微流道,而减材的方式主要是对金刚石基板进行激光烧蚀或反应等离子体刻蚀。

3.1 基于沉积工艺的金刚石微流道加工方法

目前对基于 Si 材料的微流道已有较成熟的研究,并且随着体硅刻蚀技术的发展,硅微流道的深宽比很容易超过 100,具有良好的结构基础。因此,在现有的硅微流道上沉积金刚石薄层从而制造出金刚石流道成为一种成本低廉、工艺过程相对简单的金刚石微流道加工方法。

以色列理工大学的 CHANDRAN 等在刻蚀了微通道的 Si 片上使用 HFCVD 技术沉积了多晶金刚石,成功制备了深度为 45 μm 的金刚石通道,制备的金刚石微通道结构如图 12 所示。

图12 在 Si 模具上沉积金刚石工艺制备的不同沟槽深度的微通道结构

但该沉积法加工金刚石微流道存在一些显著的问题:随着 Si 衬底上流道的深宽比增加,沉积金刚石的氢原子浓度减小,能沉积上的金刚石晶粒深度也逐渐减小,因此这种方法无法支持较大深宽比或较深的金刚石流道制备;同时多晶金刚石因为晶界的存在,杂质较多,其导热特性较单晶金刚石来说较差,导致这种沉积方式加工的金刚石流道散热性能有所欠缺。

3.2 基于激光烧蚀技术的金刚石微流道加工方法

在金刚石的材料去除加工类方法中,激光加工已经得到了较广泛的应用,在选择合适的波长、脉冲持续时间和功率后,该方法可以针对定制材料实现高质量的表面和体处理。其原理是通过外部施加能量,使金刚石的 sp3杂化键转变为较弱的 sp2杂化键,从而去除材料,塑造结构形状。

2020 年,北京航空航天大学的 YANG 等采用直流电弧等离子体喷射 CVD 法获得多晶金刚石薄膜,并将该薄膜加工成 45 mm 长、22.5 mm 宽、3 mm 厚的金刚石衬底,使用飞秒激光烧蚀技术在金刚石薄膜上制备了 37 个平行三角形微通道,通道长度为 45 mm,水力直径为 280 μm,每个通道宽度为 300 μm,高度为1500 μm(深宽比为 5)。在高热流密度(473.9~1000.4 W/cm2)条件下,研究了氨为冷却介质时微通道内流动沸腾的换热特性,散热器的散热功率密度达1000.4 W/cm2。

2022 年,该团队将飞秒激光烧蚀方法应用于多点热源的太阳能光伏电池散热系统中的散热微流道,在 351.5 W/cm2的热流密度下,控制热源表面温度在 65.9℃以下,且多点热源之间温差可以控制在 1.4℃以内。飞秒激光烧蚀金刚石微流道扫描电镜照片如图 13 所示。

图13 飞秒激光烧蚀金刚石微流道扫描电镜图

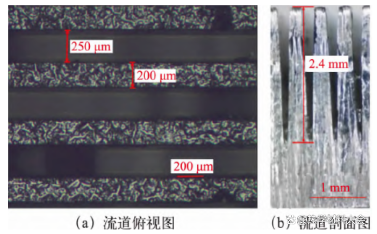

2019 年,西安交通大学的王宏兴教授课题组在HPHT 法制备的金刚石基板上使用水导激光技术加工出宽度仅为 55 μm 的金刚石沟槽,然后通过 MPCVD工艺让金刚石流道顶部外延生长厚度约 300 μm 的金刚石,从而形成封闭流道。水导激光加工后外延生长的金刚石微流道如图 14 所示。

图14 水导激光加工后外延生长的金刚石微流道

该方法制备的金刚石流道深宽比可超过 10,且深度可达 800 μm。该研究利用高于常规激光加工分辨率的水导激光加工实现了更小宽度的金刚石流道制备,但每条沟槽的加工需要激光扫描 10~20 次,激光束移动速度为 4 mm/s,在进行大尺寸散热结构批量加工时效率低且成本高。

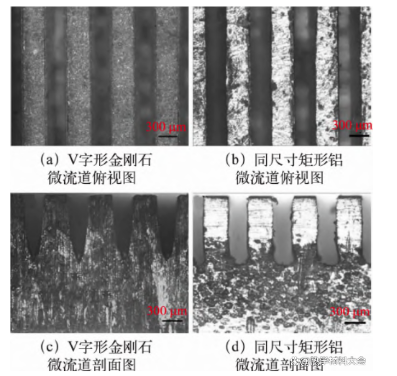

2020 年,北京科技大学的 QI 等采用 100 k W 直流电弧喷射等离子体化学气相沉积(DC Arc Plasma Jet CVD) 系统制备了 4~6 mm 的超厚金刚石膜。以CH4、H2、Ar 为反应气体,在 880℃衬底温度下开始进行沉积,通过调控甲烷气体通量实现晶粒间隙填补、抑制大尺寸柱状晶异常生长的效果。使用激光在超厚金刚石膜表面加工出 1000 μm 深、330 μm 宽(深宽比为3) 的 V 字形微流道,在热源热流密度为 40~120 W/cm2且控制热源工作温度为 100℃的情况下,测得对流传热系数为 5637.10~11 447.20 W/ (m2·K),比相同几何形状的铝微流道高 37%~73%。金刚石微流道与商用铝微流道的结构对比如图 15 所示。

图15 金刚石微流道与商用铝微流道的结构对比

3.3 基于刻蚀技术的金刚石微流道加工方法

目前通常采用激光烧蚀来实现金刚石的加工,例如切割金刚石板或金刚石刀具,以及制造微米尺度的透镜、光栅、微通道等图形结构。而随着金刚石生长技术的进步,高质量的金刚石衬底得以商业化供应,其中市售的单晶衬底通常规格可达到几平方毫米,而多晶衬底则可达到 4 英寸甚至 6 英寸晶圆规格。加工大尺寸金刚石衬底的需求对加工的速率、并行性、精细度提出了更高的要求,属于串行加工方法的激光加工逐渐显露其局限性,而反应等离子体刻蚀金刚石的微加工技术逐渐成为被广泛研究的课题。

刻蚀技术的优点在于综合利用了光刻的高分辨率、刻蚀加工的并行性以及反应等离子体刻蚀后表面的低粗糙度等,该工艺方法目前在金刚石光学器件微加工领域已有较广泛的发展。而金刚石微流道的加工制备对刻蚀深度以及刻蚀深宽比有着较高的要求,在深刻蚀的情况下,负载效应导致的刻蚀效率下降也应被考虑。

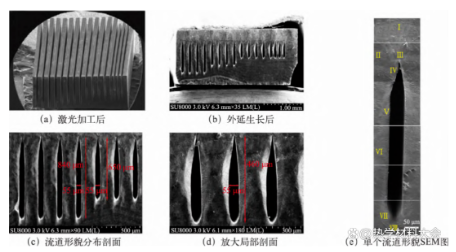

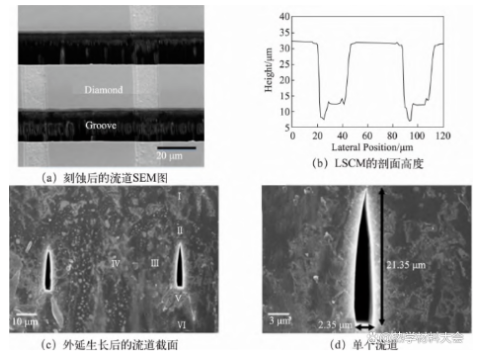

2018 年,西安交通大学的王宏兴教授课题组结合刻蚀工艺与横向外延生长工艺加工了金刚石微流道。该研究通过磁控溅射的方式在金刚石表面制备了 6 μm 厚的 Al 膜作为刻蚀硬掩模,在 ICP RIE 刻蚀工艺过程中,使用 O2和 Ar 混合的刻蚀气体配方,成功在金刚石表面加工出凹槽。在此基础上,通过MPCVD工艺使金刚石横向外延生长,最终制备得到封闭的金刚石流道。使用 ICP RIE 制备的金刚石微流道沟槽与外延生长后的微流道结构如图 16 所示。

图16 使用 ICP RIE 制备的金刚石微流道沟槽与外延生长后的微流道结构

刻蚀后形成的凹槽结构深宽比约为 1∶1,宽度及深度都约为 20 μm;经过横向外延生长的封闭流道结构深宽比提高到了 10∶1,但流道宽度由于金刚石横向生长而缩小到约 2 μm,该尺寸对用于散热的微流道来说过于狭窄,会导致较大的流体压降。

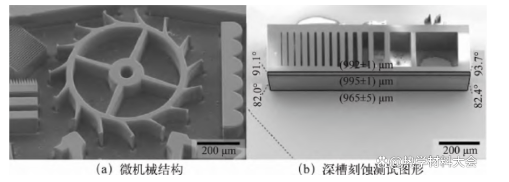

2018 年,悉尼大学的 TOROS 等仅通过氧等离子 ICP RIE 刻蚀制备的较大深度的金刚石微机械结构如图 17(a)所示。他们成功制备并释放了刻蚀深度达150 μm 的微结构,且其中槽结构深宽比可达 8∶1,侧壁较平整、垂直,深槽刻蚀测试图形如图 17(b)所示,这一研究为金刚石微流道的刻蚀加工提供了思路。

图17 金刚石 ICP RIE 深刻蚀

也有学者将研究聚焦在金刚石刻蚀工艺的控制上,2018 年,美国哈佛大学的 XIE 等利用氧等离子体对单晶金刚石有晶向选择性刻蚀的特点,提出了一种通过调控刻蚀过程中的射频偏置功率大小从而控制刻蚀暴露出的金刚石晶面的方法。研究结果表明,不同大小的偏置功率可以准确对应不同的刻蚀面角度,且当偏置功率高于 80 W 时,晶向选择性刻蚀现象基本消失,刻蚀得到的侧壁基本垂直。

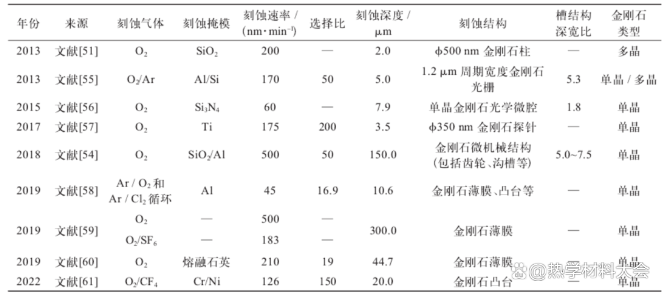

近年来报道的 ICP RIE 刻蚀金刚石的情况如表 2所示,虽然没有直接应用于散热微流道加工的研究,但金刚石刻蚀的高速率、高选择比是各项工作的共同追求,其中也包含对金刚石深刻蚀、精细结构刻蚀的研究,证明了利用刻蚀方式加工微流道具有巨大的潜力。

表2 近年来报道的 ICP RIE 刻蚀金刚石的情况

04结束语

本文基于金刚石的集成和加工技术,对近年来金刚石材料在高功率器件热管理中的发展应用情况进行了详细的综述。

金刚石的高热导率使其非常适合作为如 GaN 基 HEMT 的高热流密度器件的散热基底,解决由于散热能力不足带来的性能瓶颈问题,集成金刚石散热衬底的 HEMT 器件功率性能可以提升数倍;金刚石微通道热沉也有效地增强了电子器件的对流换热能力,显著地降低了热阻。

然而功率器件与金刚石散热衬底、金刚石微通道衬底的结合仍然存在较多问题亟待解决,主要在于以下几点:一是缺乏对不同方式所形成的功率器件与金刚石衬底之间的界面热阻深入的理论分析,导致界面热阻在实际应用中难以定量预测和控制;二是由于金刚石热膨胀系数(0.8×10-6 K-1)与常用器件(GaN: αa=5.6×10-6K-1,αc=3.2×10-6 K-1)的差异较大,在生长、键合等集成工艺实施过程中容易产生较大的热应力,器件可靠性无法得到保证;三是由于金刚石的高硬度和高化学惰性,目前的金刚石微纳加工工艺的加工效率相对较低、加工成本高,且难以实现高深宽比、 大面积微通道结构的制备,嵌入式液冷技术的优势无法完全发挥。

综上所述,应用高热导率金刚石作为热扩散层甚至微通道基底是进一步提升高功率器件散热能力的重要手段,具有巨大的研究潜力和应用价值,但目前异质界面模型、可靠性、高深宽比金刚石加工等理论和工艺技术问题亟需进一步探索与突破。

参考文献 略

手机资讯

手机资讯 官方微信

官方微信

豫公网安备41019702003646号

豫公网安备41019702003646号