以 SiC /GaN 为代表的第三代半导体功率电子学已成为当今功率电子学创新发展的主流, 超宽禁带半导体金刚石功率电子学将有可能成为下一代固态功率电子学的代表,目前金刚石半导体及器件最新进展如何?存在哪些技术痛点?未来发展态势如何?

关键词:金刚石场效应晶体管 ( FET) ; 射频 ( RF);FET; 金刚石上 GaN HEMT; 功率电子学

研究背景

在后摩尔时代, 碳基电子学的发展受到人们的广泛关注, 在纳电子学领域, 以一维的碳纳米管和二维的石墨烯为主的碳基纳电子学研究取得重大进展, 而在功率电子学领域, 以终结半导体著称的金刚石功率电子学的研究也呈现出勃勃生机, 展现出其将成为下一代功率电子学的潜力。

由于金刚石具有优异的半导体性质,近10年来行业研究热潮与进展出现许多新的突破,接下将从金刚石材料、功率二极管、功率 FET 与 IC、RF FET 和金刚石上 GaN HEMT 等几方面综述金刚石功率电子学的发展路线、最新进展和未来发展趋势。

材料研究进展

1、金刚石材料

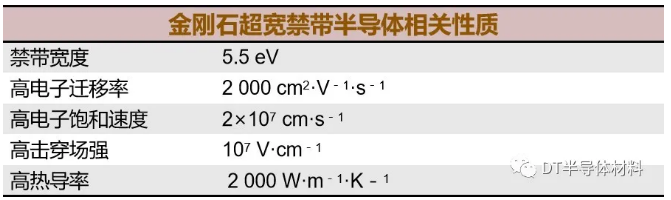

作为下一代功率电子学的候选者, 金刚石功率电子学将可能在高压大功率、高频开关、低损耗和高散热等方面优于宽禁带半导体 SiC 和 GaN 功率电子学, 为此, 要求金刚石材料的研究向大尺寸、低缺陷、低电阻率和高导热的方向发展。

1. 1 大尺寸金刚石及晶圆

目前金刚石制备方法主要有高温高压和各类化学气相沉积 ( CVD) 法。制备大尺寸金刚石及晶圆的技术主要有同质外延生长、马赛克晶圆制备和异质外延生长等技术。

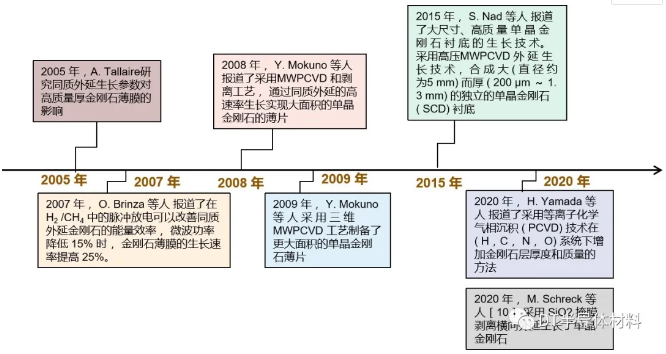

合成高质量的同质外延金刚石层是制备金刚石电子器件的重要技术之一, 其具有缺陷密度低的特点, 最大尺寸可达 0. 5 英寸 。在微波等离子化学气相沉积 ( MWPCVD) 生长技术中突破了加氮高速生长、脉冲放电高效率生长和离子注入剥离等关键技术后, 近 10 年来又实现了多方向重复的三维 MWPCVD 高速外延生长 ( 生长速率 100 μm·h-1) , 大尺寸、厚而无多晶金刚石边缘的生长和采用等离子体 CVD 在 ( H、C、 N、O)系统中 200 h 无边界连续生长等创新技术。功率电子器件的应用要求高质量的 CVD 金刚石薄膜, 其可承受很高的电场、具有相对较高的生长速率和低缺陷密度。

为了获得更大尺寸的单晶 CVD 金刚石薄片,研究人员开始尝试采用马赛克的拼接技术。近 10年来采用马赛克的拼接技术制备了 2 英寸单晶金刚石晶圆, 创新技术包括: 离子注入剥离工艺克隆籽晶片拼接; “平铺克隆”的新马赛克技术; 2 英寸马赛克拼接中适当的克隆片晶向防开裂和衬底温度均匀技术; CVD 方法共生马赛克 SCD 的工艺等。

采用异质外延技术可以在异质晶圆衬底上实现大尺寸金刚石薄膜的生长, 如 MgO、SrTiO3、Al2O3和氧化钇稳定氧化锆 ( YSZ) /Si, 其主要不足是缺陷密度高。20 世纪 90 年代后期, 开始采用铱( Ir) 薄膜上金刚石单晶异质外延生长技术 , 金刚石单晶的尺寸已达 4 英寸。近 10 年来, 在减少材料位错密度和器件应用方面的研究也取得了很大的进展。研究表明, 在 Ir 薄膜上生长几十微米金刚石后, 金刚石镶嵌块结构消失, 同时晶界的多边化网络分解为个体或凝聚的位错, 形成具有位错密度为 109 cm-2 的有缺陷的单晶。

异质外延 CVD 金刚石多晶薄膜作为功率电子器件散热的高导热热沉材料, 其具有比单晶金刚石更低的成本, 具有更广阔的应用领域, 自 20 世纪90 年代以来, 其广泛用于各类器件中作为散热材料, 其热导率超过 1 000 W·m-1·K-1, 2019 年,W. S. Lee 等人 采用 4 英寸 Si 基 CVD 金刚石多晶薄膜和 GaN HEMT 相结合的方法, 使器件的 RF 功率密度大于 23 W·mm-1, 异质外延 CVD 金刚石多晶薄膜的最大直径可达到 8 英寸。

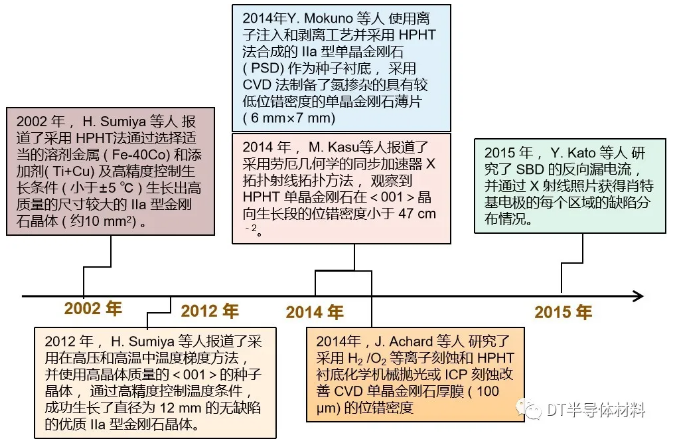

1. 2 低缺陷密度的单晶金刚石

金刚石材料中的缺陷密度对功率器件的反向漏电等性能影响较大, 对于低缺陷密度的单晶金刚石材料的研究一直是金刚石功率电子学材料的研究重点。近 10 年来, 低缺陷金刚石材料研究有了较大的进步, 包括: 采用高温高压 ( HPHT) 法可生长直径为 12 mm 的无缺陷的优质 IIa 型金刚石晶体;HPHT 单晶金刚石在<001>晶向生长段的位错密度小于 47 cm-2; 采用 CVD 制备的掺杂氮的金刚石单晶薄片的位错密度低至 400 cm-2; 采用 HPHT 法对衬底 进 行 表 面 处 理 可 有 效 降 低 厚 CVD 外 延 层( 100 μm) 的位错密度; 对 SBD 的 p 型金刚石层中的缺陷和器件反向泄漏电流的关联研究。

1. 3 金刚石材料的掺杂

金刚石材料的掺杂是形成功率器件的基础技术,p 型金刚石材料在重掺杂的低阻和厚层材料等方面实现了关键技术的突破并趋于成熟, 而掺杂难度较大的 n 型金刚石材料在近期已取得突破性进展。

对采用 CVD 方法的金刚石掺硼 ( B) 的研究始于 20 世纪 90 年代中期。1997 年, M. Werner 等人 研究了在室温下的单晶、多晶金刚石的电阻率和载流子浓度与 B 掺杂浓度之间的 Irvie 关系曲线。在金刚石的光学和电子器件的制备中, 需要与外部源的低阻路径连接以及低的欧姆接触电阻, 为此对重掺 B 金刚石的研究应运而生。重掺杂 B 低阻金刚石的技术也有了一定的进步, 如采用温度梯度方法生长了边长为 8 mm 的 IIb 型掺 B 单晶金刚石; 采用 MWPCVD 法制备了低电阻率的掺 B 金刚石薄膜 ( 电阻率为 1. 2 mΩ·cm) ; 采用热丝 CVD法制备了低阻 p+ 金刚石 ( 100) 薄膜 ( 电阻率为1 mΩ · cm, B 的掺杂浓度约为1021 cm-3) 。

在对生长掺 B 的 IIb 型金刚石研究中, 在不同的生长段和相同生长段的不同结晶参数时的金刚石中的 B 掺杂, 有时是氮杂质的非均匀分布, 这一现象 使 得 体 掺 B 金 刚 石 的 电 子 应 用 成 为 难 题。2007 年, V. D. Blank 等人 报道了在高静态压力和温度与添加 B 的 Fe-Al-C 熔液系统中, 采用温度梯度方法生长了边长为 8 mm 的 IIb 型掺 B 金刚石单晶。同年, N. Tokuda 等人 报道了对在重掺 B同质外延生长中的金刚石 ( 001) 薄膜的表面粗化研究。2015 年, S. Ohmagari 等人报道了采用热丝 CVD ( HFCVD) 法制备的低阻 p+ 金刚石 ( 100)薄膜, 其 B 的 掺 杂 浓 度 成 功 地 控 制 在 1019 ~1021 cm-3。薄膜平均表面粗糙度小于 0. 1 nm, 其室温电阻 率 低 于 1 mΩ · cm ( B 的 掺 杂 浓 度 约 为1021 cm-3) 。这些结果均表明采用 HFCVD 工艺制备器件级 p+金刚石具有一定的潜力

厚的重掺 B 金刚石材料是制备垂直结构器件的基础, 其在器件导通时可降低串联电阻。近 10年来, 对厚的重掺 B 金刚石单晶生长技术的研究有: 采 用 中 功 率 密 度 的 微 波 等 离 子 辅 助 CVD( MPACVD) 方法得到 250 μm 厚的重掺 B 独立的金刚石薄片 ( 掺杂浓度大于 1020 cm-3 ) ; 300 μm厚的重掺 B 的金刚石薄片可用于赝垂直结构 SBD;独立的 200 μm 厚的重掺 B ( 1×1020 cm-3) 的金刚石薄片可用于垂直结构的金刚石 SBD; 衬底温度和生长速率对单晶掺 B 金刚石的掺杂效率的影响;对厚的重掺 B 同质外延金刚石生长的氧效应研究;采 用 高 氧 气 流 和 高 微 波 功 率 密 度 生 长 的 厚 为500 μm、面积为 18 mm2 的重掺 B ( 掺杂浓度为 5×1019 ~ 3 × 1020 cm-3 ) 的 金 刚 石 单 晶 层, 厚( 190 μm) 的重掺 B ( 4×1020 cm-3) 的<113>晶向的 CVD 金刚石薄膜的生长和采用 HFCVD 生长的独立的 p+ ( 100) 金刚石衬底。

由于 B ( 共价半径 r1B 为 0. 088 nm) 比 C ( r1C为 0. 077 nm) 具有更大的共价半径, 将 B 引入金刚石会导致晶格参数的增大。只要在 MPCVD 外延层中 B 的原子数分数低于 0. 5%或在 HPHT 体晶体中低于 1. 5%, 其就会遵循线性插值 ( Vegard 定律) , 若高于上述原子数分数时, Vegard 的扩张也明显低于预测值。

采用 B 替代 C 的金刚石的 p 型掺杂是较容易的, 目前其技术已较成熟。相反, 对于制备金刚石基双极型器件, n 型金刚石的高电导率难以实现而且仍然是一个主要问题。近 10 年来关于 n 型金刚石的研究有: 采用 MWPECVD 在<111>晶向上形成了磷 ( P) 的掺杂浓度超过 1020 cm-3的重掺 n+金刚石薄膜;在 ( 001) 的 n 型金刚石薄膜上实现 n+ 埋层的选择性的生长; 选择生长 n+ 金刚石边栅制备的金刚石结型场效应晶体管 ( JFET) 的技术突破;实现研发金刚石双极型器件的掺 P <113>晶向 CVD金刚石的技术突破。

欧姆接触金属化是实现高性能电子器件的一个重要技术。P 的掺杂浓度为 1×1019 cm-3的 n 型金刚石薄膜, 其欧姆接触电阻约为 105 Ω·cm2。为了适应金刚石器件 n 型低欧姆接触的需要, 必须将 P的掺 杂 浓 度 提 高 到 1020 cm-3 以 上。

2012 年, T. Iwasaki 等人 通过选择生长 n+金刚石 边 栅 制 备 了 金 刚石 JFET。在 < 111 > 晶向HPHT 金刚石衬底上外延生长 0. 7 μm 厚的 p 型薄层, 通过光刻和 ICP 刻蚀形成 p 沟道, 在 p 沟道的两个侧面的<111>晶向选择性生长了掺 P 的 ( 8 ×1019 cm-3) n+ 型金刚石的栅以制备金刚石 JFET。该器件可在高温下工作, 并具有极低的泄漏电流。金刚石的<113>晶向在标准的 CVD 生长条件下是一个稳定的晶体平面, 可获得最大可用的表面积,对于功率电子学是重要的课题之一。继研究了厚的重掺 B 的<113>晶向的 CVD 金刚石薄膜的生长之后, 2019 年, M. A. P. Thaury 等 人报 道 了 掺P<113>CVD 金刚石, 并认为是发展金刚石双极器件的技术突破。在<113>型的 HPHT 金刚石衬底上采用包含 MOCVD 技术的 MPCVD 生长了掺 P 的金刚石薄膜。该< 113 >同质外延层的 P 掺杂浓度为7. 2×1016 ~ 4. 5×1019 cm-3, 厚度为 0. 6 ~ 4 μm。结果表明, 掺 P<113>晶向的外延层具有高质量且 P全部进入施主的位置, 这为发展金刚石双极器件提供了新的金刚石晶向的选择。

器件研究

2、 功率二极管

金刚石二极管的研究始于 1958 年, M. D. Bell等人报道了采用自然的 p 型金刚石形成金属点接触 的 SBD, 具 有 整 流 效 应, 直 到 1971 年,V. S. Vavilov 等人才报道了采用 B 和 P 的离子注入技术形成人造金刚石上的 p-n 结, 但离子注入技术所导致的损伤使金刚石二极管的反向击穿电压低于 500 V。近 10 年来, CVD 金刚石材料在大尺寸、低缺陷和重掺杂等方面的进展直接带动了金刚石二极管向着高击穿电压、高击穿场强、低导通电阻、高开关速率和高温工作的方向发展, SBD 和 p-n 结二极管两种类型均在开发, 其中金刚石 SBD 发展更快, 已处于初步的应用实验阶段。

由于金刚石二极管和晶体管击穿电压较低 ( 小于500 V) 的主要原因是难以控制金刚石中的掺杂物质。金刚石是地球中原子密度最高的材料, 除少数小原子 H、P、N 和 Si 元素等, 很难将其他大原子加入其晶体中。但金刚石具有高的击穿场强、低的介电常数和高的载流子迁移率, 是未来大功率器件应用的理想材料。近 10 年来金刚石 SBD 的应用越来越广泛, 如用于高温应用模拟; 高温、高功率和快开关; 金刚石 SBD 在功率变换器中的集成; 用于高功率整流天线的 RF-DC 变换器。对在功率电子学的应用中提高金刚石 SBD 的额定电流和用于 LED 的非隔离的巴克功率变换器等方面也进行了初步应用研究。

2. 2、p-n 结二极管

金刚石 p-i-n 二极管是先进的并适用于大功率应用的器件, 除了它的临界电场为 3 MV·cm-1( SiC 理论极限) 以外, 也可通过采用重掺杂层使金刚石 p-i-n 二极管的串联电阻大幅度降低。近 10年来, 金刚石 p-i-n 二极管技术有了很大的进步,如突破了具有跃迁传导机制的重掺杂的 p+ 和 n+ 层的制备; 低阻跃迁电导的金刚石 p+-i-n+ 结二极管的载流 子 输 运 机 制; 肖 特 基 金 刚 石 p-n 二 极 管( SPND) 的材料结构优化设计; 选择生长 n+ 层、p-n 结二极管的界面缺陷对反向漏电影响的机理研究; 金刚石 p-i-n 二极管的反向恢复及少子寿命研究; 金刚石肖特基p-i-n二极管 ( SPIND) 的不均匀肖特基势垒高度的机制等关键技术。这些先进的技术使 SPND 的最大正向电流密度达60000 A·cm-2( 6 V 下) , 微分比导通电阻为 0. 03 mΩ·cm2, 反向击 穿 电 压 为 55 V, n 层 的 击 穿 场 强 约 为3. 4 MV·cm-1, 在±6 V 时的整流比为 1012, 具有纳秒级的快速开关, SPIND 的正向电流密度大于300 A ·cm-2( 电压为 4 V) , 击穿电压大于 500 V,SPIND 在 873 K 高温循环后仍能保持稳定性。金刚石p-i-n 二极管在真空下可扩展到电子发射源的应用。

另外,金刚石的深掺杂能级引起其另一独特的属性,即在温度接近 300 K 时的跃迁传导机制。由于金刚石的 B 和 P 掺杂物的能级非常深, 即使在一个相对较高的掺杂浓度下, 其能级分布为扩展状态而无重叠。300 K 时, 在 p 型和 n 型单晶金刚石中, 当掺杂浓度超过 1019 cm-3时, 在传导系统中跃迁传导为主 导, 导 致 电 阻 率 大 幅 度 下 降。

读后总结

目前金刚石产业化道路任重道远,目前存在问题是金刚石的高效体掺杂尚未解决,制造P型晶体管容易、制造n型晶体管困难。以及大尺寸晶圆制备、高平整度、高均匀性材料外延技术等瓶颈……但我国半导体自主创新离不开科研人员与产业界的共同努力,为中国芯而奋斗!

备注:内容节选于《超宽禁带半导体金刚石功率电子学研究的新进展》

手机资讯

手机资讯 官方微信

官方微信

豫公网安备41019702003646号

豫公网安备41019702003646号