1 异质外延单晶金刚石

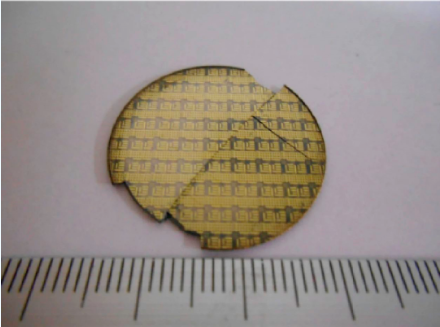

微波等离子体化学气相沉积(MPCVD)是高质量单晶金刚石制备的主流方法。根据衬底选择可将其分为同质外延和异质外延两种。同质外延以单晶金刚石为衬底,通过三维生长技术、马赛克拼接技术来获得大面积单晶。目前利用马赛克拼接技术可获得尺寸为40 mm×60 mm的单晶金刚石衬底。异质外延的外延材料与衬底材料不同,金刚石单晶异质外延技术历经多年发展,从起初的外延金刚石晶粒,到完整的异质外延单晶金刚石薄膜,如今已能外延生长近4英寸的单晶金刚石衬底(见图1),晶体质量也在不断提升。

图1 当前最大尺寸的异质外延单晶金刚石衬底

MgO和SrTiO3与金刚石的热膨胀系数差异大,所以当达到适宜金刚石外延的温度时(图2中虚线所示),沉积在氧化物衬底上的金刚石薄膜内的高应力会导致金刚石容易碎裂或是从衬底上脱落。Al2O3和Si衬底则具有成本低、可获得大面积衬底、晶体质量高等优势,而且与金刚石热失配相对较小,因而成为了异质外延单晶金刚石的主流衬底。

图2 不同衬底与沉积的金刚石之间的热应力-沉积温度变化关系

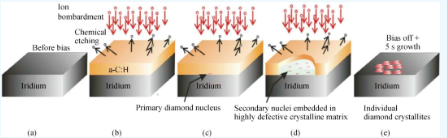

如图3所示,在BEN过程刚开始时,Ir表面首先生成一层非晶碳层(见图3(a)),在电场加速的作用下,被微波激发的碳离子源源不断地被注入到Ir的亚表面直至饱和,而当碳的浓度继续升高时,Ir亚表面的C原子就会析出形成初级金刚石核。初级金刚石核形成之后,通过C原子之间的相互作用力规范其周围的C原子,形成排列规则的金刚石核(见图3(c))。而在偏压关掉后,以及金刚石快速生长过程开始的5~10 s内,Ir表面的非晶碳便会在富氢的环境下被刻蚀掉。

图3 金刚石BEN过程示意图

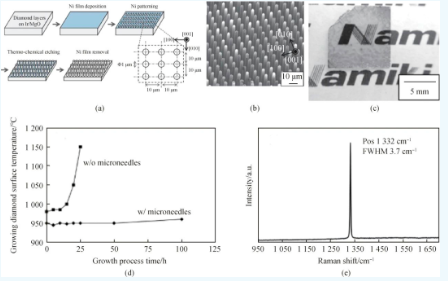

实验成功制备了尺寸为10 mm×10 mm×1 mm的单晶金刚石衬底,其拉曼半峰全宽为3.7 cm-1,晶体质量较好。

图4 (a)金刚石微米针制备工艺流程;(b)经 Ni化学刻蚀后形成的金刚石微米针;(c)10 mm×10 mm×1 mm异质外延单晶金刚石衬底;(d)有、无微米针衬底在生长过程中的温度变化对比;(e)金刚石衬底的拉曼光谱图

该方法有以下优点:1)利用ELO提高了金刚石晶体质量;2)金刚石微米针可以有效缓解金刚石和氧化物由于晶格失配所产生的应力,解决了快速生长过程中因衬底翘曲而散热不佳的问题;3)可以实现金刚石与衬底的自动剥离。此方法或可在所得金刚石衬底上进行多次迭代,不断提高金刚石晶体质量。

图5 1英寸异质外延金刚石衬底[25]

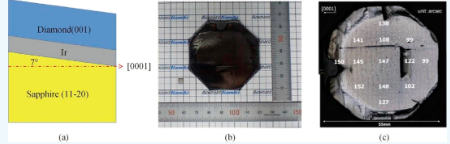

2022年,Kasu团队在表面偏<001>方向7°的α-Al2O3衬底上进行金刚石的异质外延生长,其衬底结构如图6(a)所示。实验发现,金刚石在快速生长过程中呈台阶生长模式,其晶体内部的张应力被释放,改善了结晶质量,成功地制备了尺寸2英寸的单晶金刚石衬底(见图6(b))

图6 (a)离轴生长示意图;(b)2英寸异质外延单晶金刚石衬底;(c)2英寸单晶金刚石(004)面的XRD摇摆曲线半峰全宽全谱图

如图7所示,加入含有金属W的缓冲层后,金刚石表面刻蚀坑数量明显减少,位错密度大幅降低。

图7 经H2/O2等离子体处理后的MPCVD异质外延金刚石表面SEM照片

2 基于异质外延单晶金刚石衬底的功率电子器件

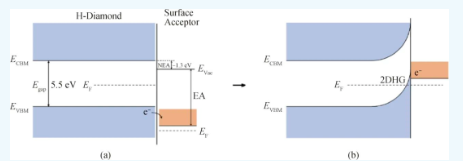

金刚石的n型掺杂技术面临着施主激活能高的问题,其技术还在探索中。目前的金刚石基MOSFET主要是利用氢终端作为导电沟道来制备。氢终端金刚石暴露在空气、二氧化氮、臭氧,或是和一些过渡属氧化物如V2O5、MoO3等接触时,表面电子将会转移到表面吸附物中,从而引起表面能带上弯,进而在表面形成一层二维空穴气(2DHG)。

图8 氢终端金刚石表面形成二维空穴气的能带示意图[59]

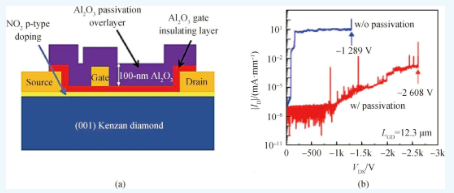

器件结构如图9所示。其最大源漏电流为-288 mA/mm。实验证明,100 nm Al2O3钝化层有效地抑制了器件的漏电,关态下实现了-2608 V的击穿电压,击穿电场为2 MV·cm-1,这与目前SiC、GaN基MOSFET相当。

图9 100 nm Al2O3覆盖层的MOSFET结构截面示意图(a)和关态下的ID-VDS(b)

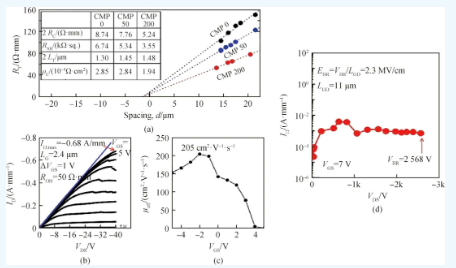

2022年,Kasu等利用化学机械抛光(CMP)技术对异质外延单晶金刚石衬底进行抛光来提高表面平整度和降低缺陷。经过200 h的CMP处理后,金刚石表面粗糙度为0.04 nm,氢终端表面方块电阻大小为3.55 kΩ/sq,结果如图10(a)所示。

图10 (a)不同CMP处理下的金/氢终端金刚石传输线模型参数;(b)MOSFET开态下的ID-VDS曲线;(c)有效迁移率;(d)关态下的ID-VDS曲线

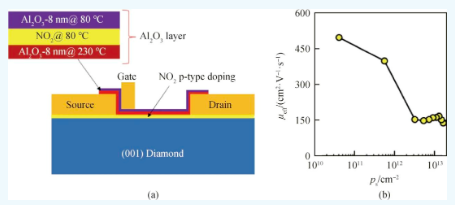

同年,该研究团队制备了“调制掺杂”金刚石MOSFET。如图11所示,通过在8 nm的Al2O3栅极介质层上方进行二氧化氮掺杂,将NO2和氢终端沟道进行分离,迁移率提高到496 cm2/(V·s),击穿电压达到-3326 V,最大漏极电流密度为-0.42 A/mm,BFOM为820.6 MW/cm2,该研究证明了异质外延单晶金刚石有望运用于射频功率器件。

图11 (a)MOSFET横截面结构示意图;(b)调制掺杂的MOSFET有效迁移率随载流子浓度的变化

如图12所示,p-i-n二极管的电流-电压特性表现出良好的整流特性。增大正向电流导致缺陷发光的积分强度呈亚线性增加,而自由激子发光的积分强度呈超线性增加。这一显著的趋势与在传统的HTHP合成金刚石衬底上用同质外延生长薄膜制备的p-i-n二极管所观察到的趋势相同。预示着异质外延单晶金刚石衬底在未来金刚石基电子器件中的潜力。

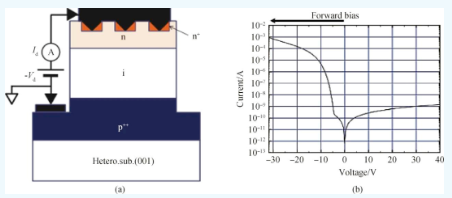

图12 (a)p-i-n器件结构以及测试原理图;(b)二极管正向导通特性

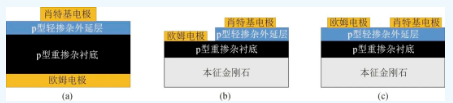

由于金刚石的n型掺杂技术尚未成熟,所以目前的金刚石基肖特基二极管主要通过p型金刚石和金属形成肖特基结实现。从结构上可分为垂直型、准垂直型和横向型,其结构如图13所示。

图13 (a)垂直型肖特基二极管;(b)准垂直型肖特基二极管;(c)横向型肖特基二极管

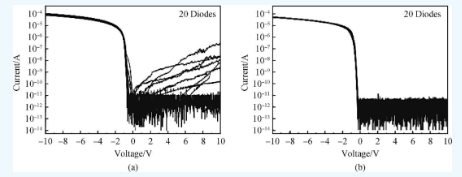

2021年,Sittimart等通过插入含有金属钨的缓冲层以抑制缺陷。在边长为5 mm的异质外延晶体上制备了准垂直肖特基势垒二极管。插入缓冲层后,面内均匀性得到改善,所有肖特基二极管均表现出优异的整流效果,漏电流得到抑制,如图14所示。

图14 没有(a)和有(b)缓冲层的20个肖特基二极管在室温下的I-V特性

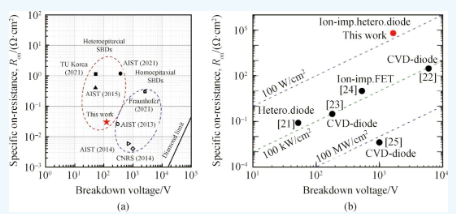

图15对比了近年来所报道的金刚石肖特基二极管的电学性能。横坐标为击穿电压,纵坐标为比导通电阻。从图15可以看出,基于异质外延单晶金刚石衬底的肖特基二极管的性能总体上不如同质外延金刚石衬底,这主要是因为目前的异质外延单晶金刚石衬底的晶体质量难以达到同质外延的水平。进一步提升异质外延单晶金刚石晶体质量是提升器件性能的关键。

图15 金刚石肖特基二极管性能对比图

手机资讯

手机资讯 官方微信

官方微信

豫公网安备41019702003646号

豫公网安备41019702003646号